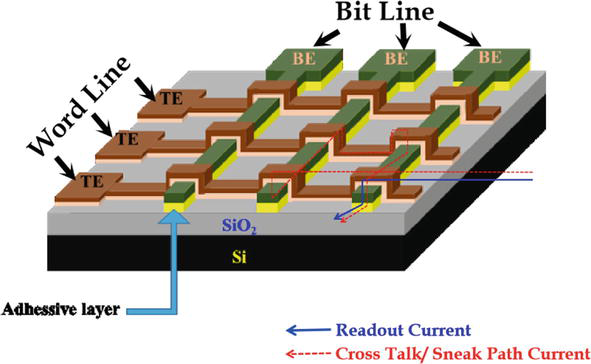

Resistive Memory with Functional Duality-Non Volatile Emerging Memory & Nano Biosensors | IntechOpen

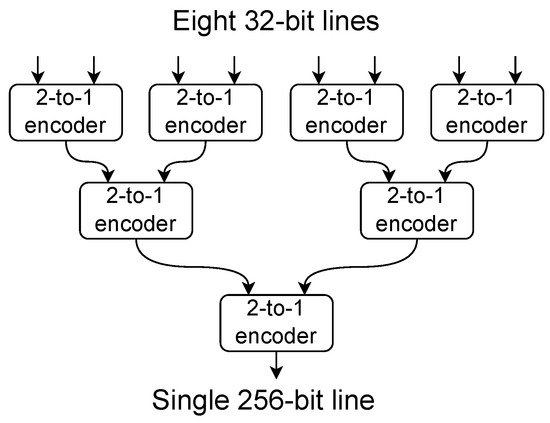

Electronics | Free Full-Text | Scalable Data Concentrator with Baseline Interconnection Network for Triggerless Data Acquisition Systems

1G DRAM cell with diagonal bit-line (DBL) configuration and edge operation MOS (EOS) FET | Semantic Scholar

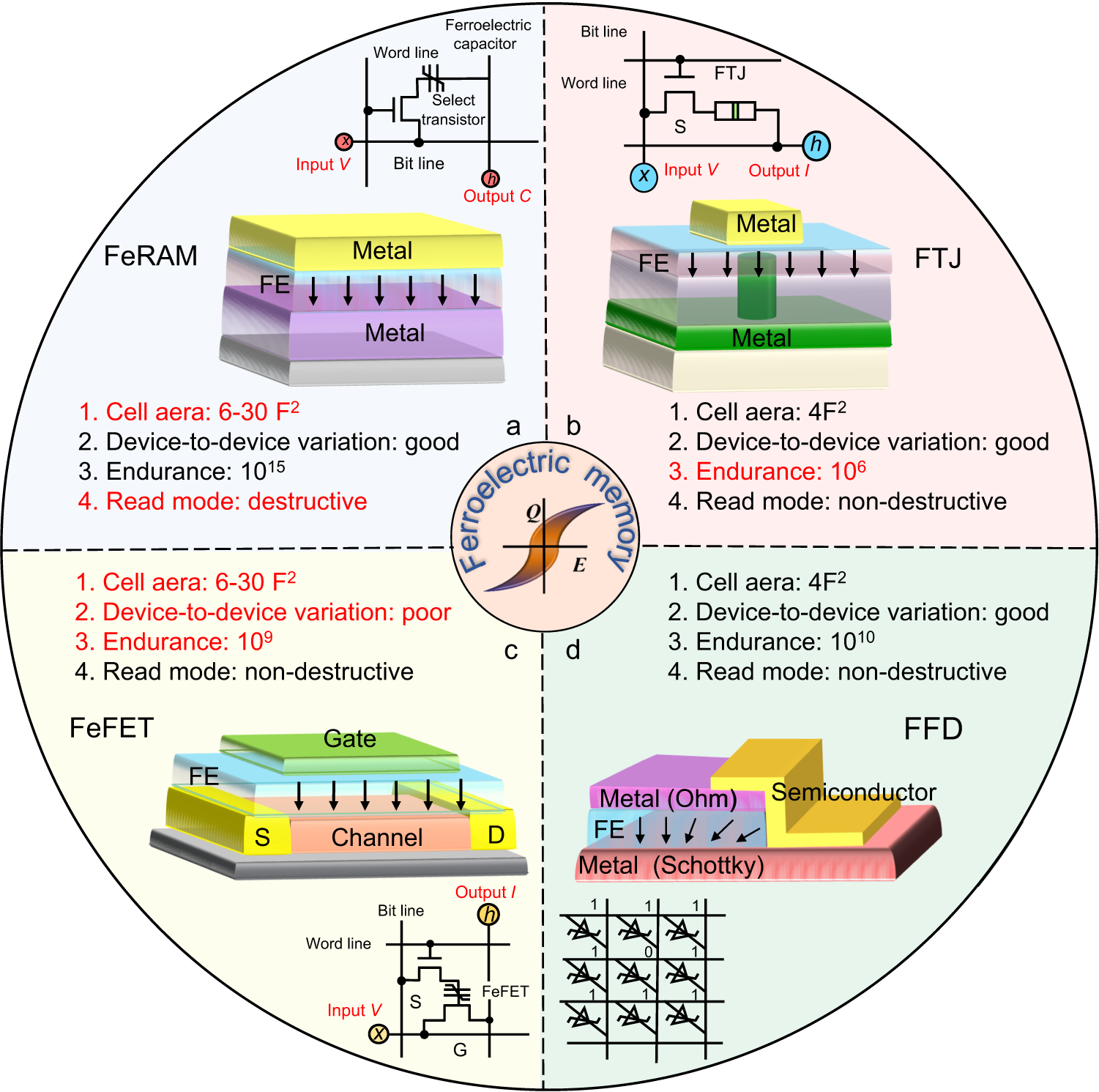

FeRAM structure and polarization: (a) a 1T1C-based structure (FeRAM... | Download Scientific Diagram

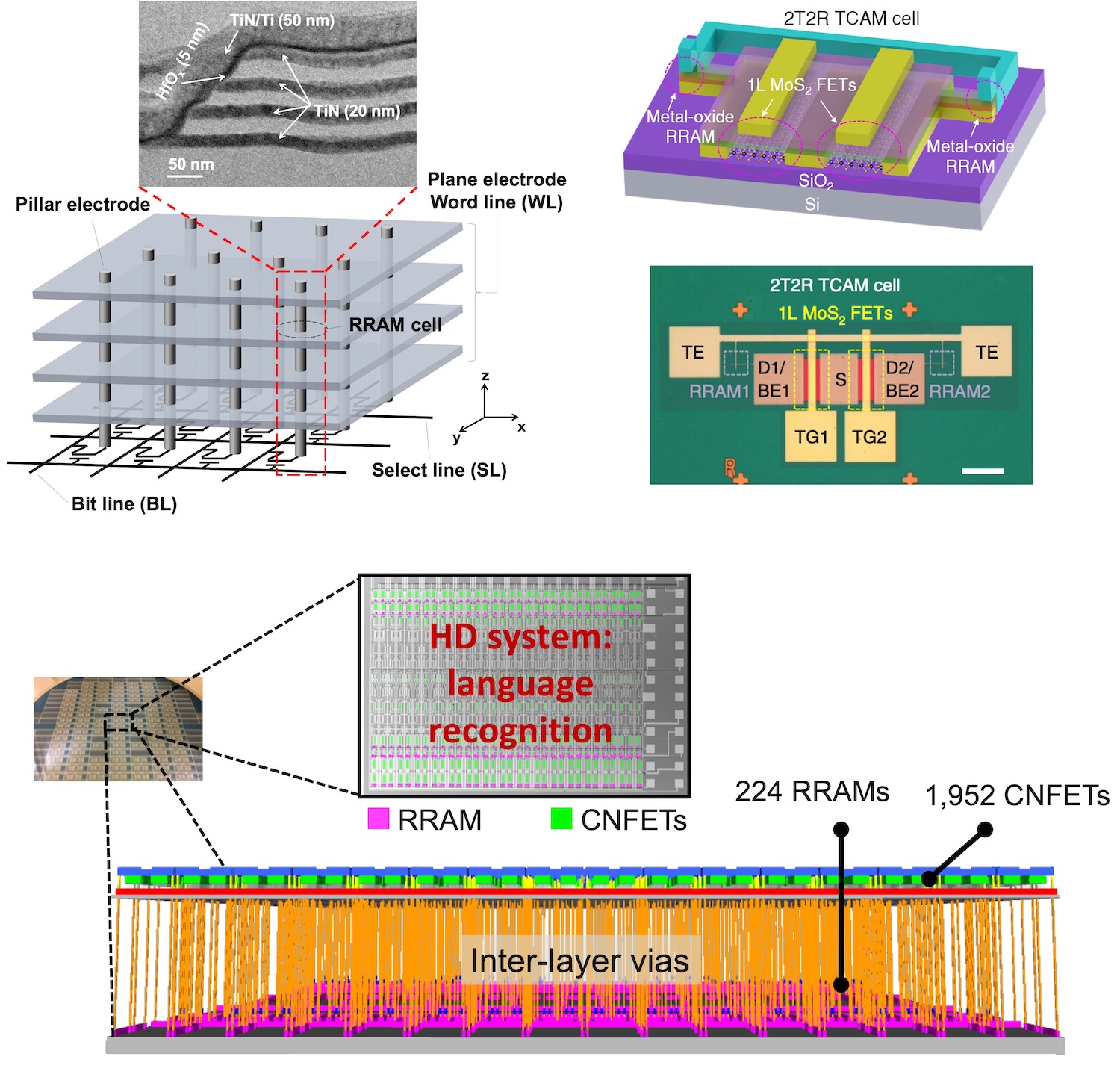

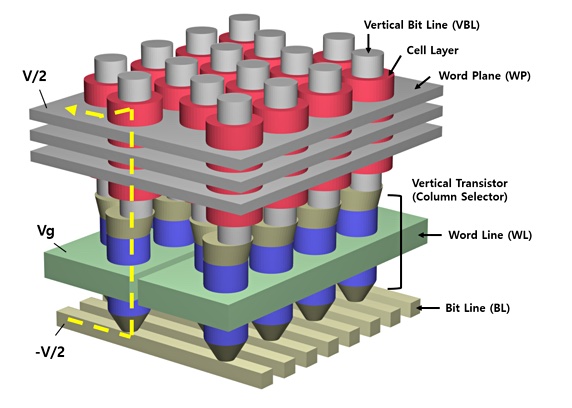

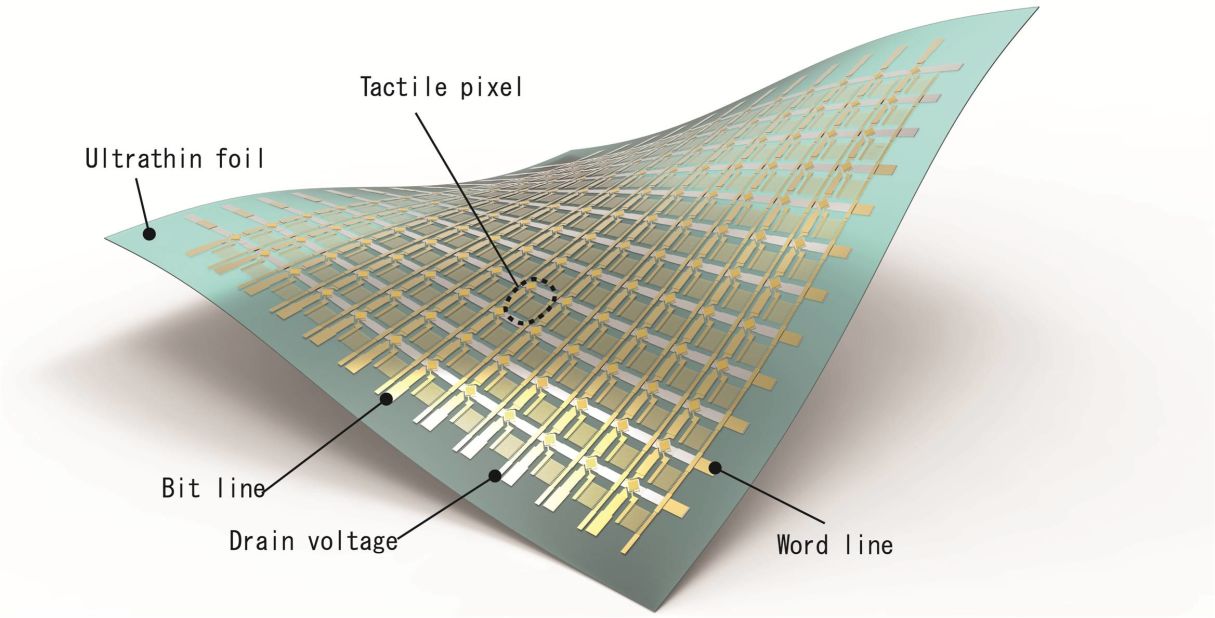

Resistive Random Access Memory (RRAM) Technology: From Material, Device, Selector, 3D Integration to Bottom-Up Fabrication | SpringerLink